I know I messed up, but I want to find out what exactly is going on and if it is still fixable. I did the following between 2 Samsung chromebook pro.

I first used the script to upgrade the spi flash to UEFI for chromebook #1.

I backup the whole spi flash of chromebook #1 using a clip flash reader and just write it into another chromebook pro (chromebook #2) with a seemingly same main board inside. For chromebook #2, I did not upgrade using the script, but just programmed it with the rom i backed up from chromebook #1. I think I did not even remove the write protection screw. Now chromebook #2 will boot, but it seems like it is blank for 30 second before booting. When it has the blank screen, back light did not even turn on.

I then tried to restore the original rom of chromebook #2, but I realized when I back up the rom, I messed up and it saved nothing.

What is going on during the first 30 second? Is there someway I can fix this?

you didn’t run the script, so the WP registers on the chip are still set, likely causing RAM training to fail and be re-run on each boot.

remove the WP screw, run the script from Linux, and re-flash the firmware. On the 2nd boot after it should have a normal boot time.

Thanks! It does sounds like what it is happening. I will have to run the script to see if it works.

I reinstalled the firmware with the script, but it did not clear the 30 second delay.

There is actually complications. I replaced the RAM chip to 16GB instead of the original 4GB. And I modified the firmware to represent it. As a result when I use the script, it does not work right away. I updated the firmware with the script and power off. Read the flash, modify it and then write it back before restarting. However, after restarting a few times, it is still the same. There is no improvement. I then follow the step on your site from disabling FW WP with the command

sudo flashrom --wp-status --programmer internal

and get the following result

Does this mean the register is not cleared?

Would it has anything to do with GBB flag?

flashrom v1.3.0 on Linux 6.8.5-301.fc40.x86_64 (x86_64)

flashrom is free software, get the source code at https://flashrom.orgUsing clock_gettime for delay loops (clk_id: 1, resolution: 1ns).

Cannot open file stream for /dev/mtd0

coreboot table found at 0x7aa1c000.

Found chipset “Intel Skylake Y Premium”.

This chipset is marked as untested. If you are using an up-to-date version

of flashrom and were (not) able to successfully update your firmware with it,

then please email a report to [email protected] including a verbose (-V) log.

Thank you!

Enabling flash write… Warning: Setting BIOS Control at 0xdc from 0x8b to 0x89 failed.

New value is 0x8b.

SPI Configuration is locked down.

FREG0: Flash Descriptor region (0x00000000-0x00000fff) is read-only.

FREG1: BIOS region (0x00200000-0x00ffffff) is read-write.

FREG2: Management Engine region (0x00001000-0x001fffff) is locked.

Not all flash regions are freely accessible by flashrom. This is most likely

due to an active ME. Please see ME (Management Engine) — flashrom documentation for details.

At least some flash regions are read protected. You have to use a flash

layout and include only accessible regions. For write operations, you’ll

additionally need the --noverify-all switch. See manpage for more details.

OK.

Found Programmer flash chip “Opaque flash chip” (16384 kB, Programmer-specific) on internal.

Failed to get WP status: WP operations are not implemented for this chip

lol, and you didn’t think that was relevant to mention before now?

please provide a cbmem log, both -1 and -t outputs, so I can see what’s happening

it means that flashrom can’t read the status registers.

absolutely not, the are a construct of the stock firmware, they do not exist anymore.

In the beginning, before I change the RAM from 4GB to 16GB, I flashed the backup of the UEFI from chromebook #1 and the 30 sec delay is already there. So I didnt link it to the RAM change, but I am not too good with the firmware so I could be wrong.

Here is the cbmem log

CBMEM table of contents:

NAME ID START LENGTH

0. FSP MEMORY 46535052 7abfe000 00400000

- CONSOLE 434f4e53 7abde000 00020000

- RO MCACHE 524d5346 7abdd000 000004f4

- TIME STAMP 54494d45 7abdc000 00000910

- MEM INFO 494d454d 7abdb000 00000f48

- AFTER CAR c4787a93 7abce000 0000d000

- RAMSTAGE 9a357a9e 7aa76000 00158000

- REFCODE 04efc0de 7aa48000 0002e000

- SMM BACKUP 07e9acee 7aa38000 00010000

- SMM COMBUFFER 53534d32 7aa28000 00010000

- IGD OPREGION 4f444749 7aa24000 000030c8

- COREBOOT 43425442 7aa1c000 00008000

- ACPI 41435049 7a9f8000 00024000

- TCPA TCGLOG 54445041 7a9e8000 00010000

- SMBIOS 534d4254 7a9e0000 00008000

- FSP RUNTIME 52505346 7affebe0 00000004

- VPD 56504420 7affea60 0000016b

- FMAP 464d4150 7affe8c0 00000188

- POWER STATE 50535454 7affe880 00000040

- FSPM VERSION 56505346 7affe860 00000004

- ROMSTAGE 47545352 7affe840 00000004

- ROMSTG STCK 90357ac4 7affe780 000000a8

- ACPI GNVS 474e5653 7affe740 00000038

- TPM PPI 54505049 7affe5e0 0000015a

45 entries total:0:1st timestamp 14,212 (0)

11:start of bootblock 21,528 (7,315)

12:end of bootblock 24,044 (2,516)

13:starting to load romstage 24,045 (0)

14:finished loading romstage 24,710 (664)

1:start of romstage 24,960 (250)

970:loading FSP-M 30,817 (5,856)

2:before RAM initialization 31,308 (491)

950:calling FspMemoryInit 33,686 (2,377)

951:returning from FspMemoryInit 25,813,292 (25,779,606)

550:starting to load ChromeOS VPD 25,814,344 (1,051)

551:finished loading ChromeOS VPD (RO) 25,814,556 (212)

3:after RAM initialization 25,831,423 (16,866)

4:end of romstage 25,838,874 (7,451)

100:start of postcar 25,840,891 (2,017)

101:end of postcar 25,840,892 (0)

8:starting to load ramstage 25,840,897 (5)

15:starting LZMA decompress (ignore for x86) 25,840,916 (18)

16:finished LZMA decompress (ignore for x86) 25,884,288 (43,372)

9:finished loading ramstage 25,884,505 (216)

10:start of ramstage 25,884,536 (31)

971:loading FSP-S 25,884,637 (101)

17:starting LZ4 decompress (ignore for x86) 25,884,647 (9)

18:finished LZ4 decompress (ignore for x86) 25,901,673 (17,025)

30:device enumeration 25,914,793 (13,120)

954:calling FspSiliconInit 25,917,963 (3,169)

955:returning from FspSiliconInit 25,944,941 (26,977)

40:device configuration 25,946,828 (1,887)

956:calling FspNotify(AfterPciEnumeration) 25,950,365 (3,536)

957:returning from FspNotify(AfterPciEnumeration) 25,950,497 (132)

50:device enable 25,950,502 (4)

60:device initialization 25,951,216 (713)

15:starting LZMA decompress (ignore for x86) 25,953,406 (2,190)

16:finished LZMA decompress (ignore for x86) 25,953,775 (368)

70:device setup done 27,274,788 (1,321,013)

75:cbmem post 27,274,807 (18)

80:write tables 27,274,826 (18)

85:finalize chips 27,281,705 (6,879)

90:starting to load payload 27,282,971 (1,265)

15:starting LZMA decompress (ignore for x86) 27,283,097 (126)

16:finished LZMA decompress (ignore for x86) 27,785,074 (501,977)

958:calling FspNotify(ReadyToBoot) 27,785,164 (89)

959:returning from FspNotify(ReadyToBoot) 27,786,215 (1,051)

960:calling FspNotify(EndOfFirmware) 27,786,216 (0)

961:returning from FspNotify(EndOfFirmware) 27,786,267 (50)

99:selfboot jump 27,786,696 (429)Total Time: 27,772,460

I reboot a few times and get the log again. It seems that it is a bit faster, but is still longer than normal.

CBMEM table of contents:

NAME ID START LENGTH

0. FSP MEMORY 46535052 7abfe000 00400000

- CONSOLE 434f4e53 7abde000 00020000

- RO MCACHE 524d5346 7abdd000 000004f4

- TIME STAMP 54494d45 7abdc000 00000910

- MEM INFO 494d454d 7abdb000 00000f48

- AFTER CAR c4787a93 7abce000 0000d000

- RAMSTAGE 9a357a9e 7aa76000 00158000

- REFCODE 04efc0de 7aa48000 0002e000

- SMM BACKUP 07e9acee 7aa38000 00010000

- SMM COMBUFFER 53534d32 7aa28000 00010000

- IGD OPREGION 4f444749 7aa24000 000030c8

- COREBOOT 43425442 7aa1c000 00008000

- ACPI 41435049 7a9f8000 00024000

- TCPA TCGLOG 54445041 7a9e8000 00010000

- SMBIOS 534d4254 7a9e0000 00008000

- FSP RUNTIME 52505346 7affebe0 00000004

- VPD 56504420 7affea60 0000016b

- FMAP 464d4150 7affe8c0 00000188

- POWER STATE 50535454 7affe880 00000040

- FSPM VERSION 56505346 7affe860 00000004

- ROMSTAGE 47545352 7affe840 00000004

- ROMSTG STCK 90357ac4 7affe780 000000a8

- ACPI GNVS 474e5653 7affe740 00000038

- TPM PPI 54505049 7affe5e0 0000015a

45 entries total:0:1st timestamp 17,937 (0)

11:start of bootblock 25,717 (7,779)

12:end of bootblock 28,278 (2,561)

13:starting to load romstage 28,278 (0)

14:finished loading romstage 28,951 (672)

1:start of romstage 29,204 (253)

970:loading FSP-M 34,455 (5,250)

2:before RAM initialization 34,951 (496)

950:calling FspMemoryInit 37,331 (2,379)

951:returning from FspMemoryInit 15,247,222 (15,209,891)

550:starting to load ChromeOS VPD 15,248,288 (1,066)

551:finished loading ChromeOS VPD (RO) 15,248,503 (214)

3:after RAM initialization 15,249,318 (814)

4:end of romstage 15,256,813 (7,494)

100:start of postcar 15,258,831 (2,018)

101:end of postcar 15,258,831 (0)

8:starting to load ramstage 15,258,837 (5)

15:starting LZMA decompress (ignore for x86) 15,258,855 (18)

16:finished LZMA decompress (ignore for x86) 15,302,206 (43,350)

9:finished loading ramstage 15,302,466 (260)

10:start of ramstage 15,302,497 (31)

971:loading FSP-S 15,302,599 (101)

17:starting LZ4 decompress (ignore for x86) 15,302,608 (9)

18:finished LZ4 decompress (ignore for x86) 15,319,812 (17,204)

30:device enumeration 15,332,827 (13,014)

954:calling FspSiliconInit 15,335,998 (3,171)

955:returning from FspSiliconInit 15,362,871 (26,872)

40:device configuration 15,364,760 (1,888)

956:calling FspNotify(AfterPciEnumeration) 15,368,292 (3,532)

957:returning from FspNotify(AfterPciEnumeration) 15,368,411 (118)

50:device enable 15,368,415 (4)

60:device initialization 15,369,127 (711)

15:starting LZMA decompress (ignore for x86) 15,371,304 (2,177)

16:finished LZMA decompress (ignore for x86) 15,371,673 (369)

70:device setup done 16,702,218 (1,330,545)

75:cbmem post 16,702,237 (18)

80:write tables 16,702,255 (18)

85:finalize chips 16,709,245 (6,990)

90:starting to load payload 16,710,510 (1,264)

15:starting LZMA decompress (ignore for x86) 16,710,636 (126)

16:finished LZMA decompress (ignore for x86) 17,212,255 (501,618)

958:calling FspNotify(ReadyToBoot) 17,212,329 (74)

959:returning from FspNotify(ReadyToBoot) 17,213,320 (991)

960:calling FspNotify(EndOfFirmware) 17,213,321 (0)

961:returning from FspNotify(EndOfFirmware) 17,213,371 (50)

99:selfboot jump 17,213,798 (426)Total Time: 17,195,841

I need cbmem -1 (dash one).

the timestamp log shows that RAM training is being run every boot, that is your 25s:

951:returning from FspMemoryInit 25,813,292 (25,779,606)

need the cbmem console log (link to pastebin, DO NOT PASTE HERE) to try and figure out why

I messaged you the pastebin link. Thanks for helping me out.

I used external programmer writing Google stock firmware back to the spi flash. The firmware backup was from another machine. Since I mod the ram to 16gb, I need to modify the firmware to make it boot. ![]()

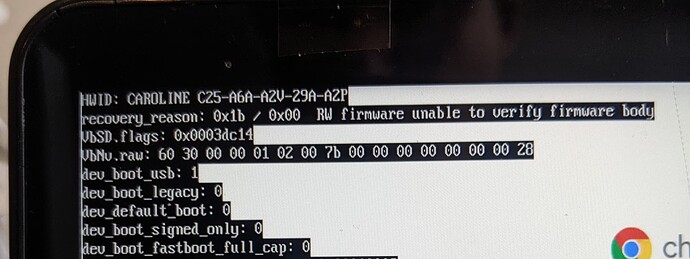

Upon using recovery to restore to Chromeos, (need to modify it again after restore to boot, it still can only boot back to recovery screen. Ctrl d or vt2 doesn’t work. I then do the ctrl I to get info. See in the attachment.

It said rw firmware unable to verify firmware body. It definitely has soemthing to do with modifying the firmware to represent the 16gb. Is there a way to rebuild it to make it works? I am not too good with rebuilding firmware, but from what I read in your site, I can only configure what model but not specify the ram?

I tried fedora and Ubuntu flashrom updated to the latest version and both seem like they doesn’t work to read wp status.

There are a few things that I want to find out.

- Is the wp protection register located within the spi flash?

- If it is, then when I write with external clip on programmer, shouldn’t it program with the wp protect register disable already?

- Perhaps it has something to do with vpd data not matching with something somewhere else? Like with the ec flash or seething else?

- yes

- no, modifying the SPI status registers is not automatic, just like with internal flashing.

- is has absolutely nothing to do with VPD. VPD is completely optional. it contains the serial # and LAN MAC address for devices with a ethernet port. It’s completely unused otherwise

Thanks for the information.

The only option I see is possible is to remove the upgrade ram and put it back into the original 4gb and then start the process from the beginning from chromeos. It seems that I am locked out from accessing the wp protection register.

It was be a project for another time. ![]()

But I am happy that at least it is functional after booting up.

I just tried using linux mint and complied the ChrumiumOS fork of the flashrom and can finally see the wp-status.

It seems that I can wp-status, wp-disable, but not wp-enable.

Is the flash descriptor region supposed to be read only?

what does “it seems” mean?

the IFD is locked on all production ChromeOS devices

It means when I run wp-disable and wp-status, it works, but when I try wp-enable, it fails. So the wp status register is working as it should be?

I can’t diagnose ‘it fails,’ give me the error output at least

upstream flashrom and ChromeOS flashrom have different levels of support for WP functions

Is the one from pastepin I posted earlier the error output? Or it is a log file?

After months of investigation, I finally come to the conclusion that this issue is caused by ‘dirty’ ME region. When you move the firmware including the ME region from one board to anther, you need to clean the ME region otherwise you will get all kind of problem.

ME region has 3 stages. It is unconfigured, configured, initialized.

When you get the firmware from a running system, the ME is initialized to the specific machine. You need to clean the ME region to get it back to configured statge to put on anther machine.

After I cleaned up the ME region, the machine bootup normally without delay.

If you have the same problem, you can follow this guide here to clean up the ME region.